简介

我在做行业咨询工作的过程中经常遇到三大产品故障,分别是辐射发射、辐射敏感度和静电放电。对数百种产品进行审查和测试后,我总结出产品未能通过测试的五大原因(按发生顺序排列):

- PCB设计——布局和叠层结构存在问题。

- 电缆屏蔽端接和猪尾巴效应(Pigtail)——电缆屏蔽层并未端接到外壳上或者没有屏蔽的产品缺少共模过滤,以及采用了屏蔽层Pigtail。

- 返回路径不连续——高频时钟或信号在返回路径上跨越间隙Gap。

- 电源分配网络设计——电源分配网络(PDN)设计欠妥。

- 屏蔽设计——屏蔽外壳内的开口或槽过长。

PCB设计

达到EMC/EMI合规性的首要因素与PCB设计有关。需要注意的是,在设计符合EMC标准的PCB时,并非所有信息来源(书籍、杂志文章或制造商的应用说明)都是正确的,尤其是10年前的信息。此外,许多“经验法则”都基于特定的设计,可能不适用于未来或有具体需求的设计。一些经验法则可能只是碰巧行得通。

设计PCB必须从物理角度出发,最重要的考虑因素是必须将高频信号、时钟和电源分配网络(PDN)设计为传输线,也就意味着传输的信号或能量以电磁波的形式传播。PDN是一种特殊情况,因为它们必须承载直流电流,并且能够以最小的同步开关噪声 (Simultaneous Switching Noise ,简称SSN) 为开关瞬态提供能量。PDN的特征阻抗设计为非常低的阻抗(通常为0.1~1.0欧姆)。另一方面,信号走线通常设计为具有50~100欧姆的特征阻抗。

了解PCB设计其实就是了解两个重要概念:所有电流都在回路中流动、高频信号通过传输线以电磁波形式传播。这两个概念密切相关、相互结合。

回路中的电流

电路理论表明,电流在回路中从源端流向负载,再返回到源端。许多产品之所以出现故障,是因为没有明确定义电流返回路径,在某些情况下,返回路径甚至是间断的。电路设计人员经常忽略的问题是需要定义高频信号返回至源端的路径。仔细想想,我们甚至没有在原理图上画出这些返回路径,只是用一系列不同的“接地”符号表示回路。

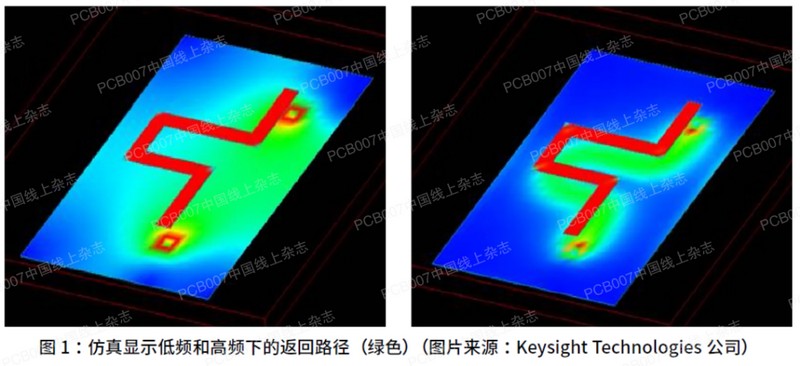

什么是“高频”?一般来讲,高于50~100kHz的频率称之为高频。当频率低于这个区间时,返回电流倾向于沿着最短路径返回至源端(电阻最小路径)。当频率高于此区间时,返回电流往往会直接沿着信号走线下方并返回至源端(阻抗最小路径),如图1所示。

为了降低EMI,我们需要最大程度减小这些回路的面积。未定义的返回路径通常会导致从源端到负载再到源端的电流回路过大。这些大电流回路开始看起来像环形天线,将噪声电流耦合到产品或系统里“类似天线”的结构当中,例如电缆。

有些电路板设计出错的地方是当高dV/dt返回信号(例如来自低频 DC/DC 开关模式转换器的信号或来自数字逻辑和时钟返回信号的高di/dt 信号)会与 I/O电路返回电流、敏感的射频RF模块(尤其是接收端)、敏感的模拟返回电流混合到一起。要了解设计明确的信号和电源返回路径的重要性。这就是为什么要在高频信号下使用实心返回平面,然后将电路板上的数字信号、电源和模拟电路隔离开来的原因。

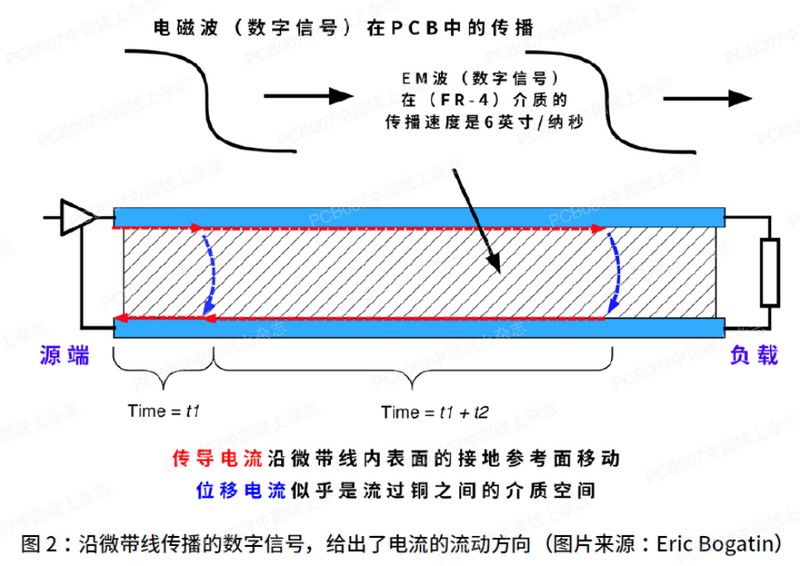

信号的移动方式——在大于50~100kHz的频率下,数字信号开始在传输线中以电磁波的形式传播。高频信号(图2)沿传输线(例如回路平面上的电路走线)传播,波前部分在铜走线中引入了传导电流,并沿返回平面返回。当然,这种传导电流不能通过PCB电介质流动,但波阵面的电荷会排斥返回平面上的类似电荷,这就是“看起来”好像有电流在流动的原因。这与电容器似乎“通过”交流电的原理相同,Maxwell将这种效应称为“位移电流”(Displacement Current)。

信号的波前传播速度是光速的几分之一,具体取决于材料的介电常数,而传导电流则由高密度的自由电子组成,以大约1厘米/秒的速度移动。但由于电场中沿铜分子传播的“扭结”,电场的传播速度接近光速。重要的是,这种传导和位移电流的组合必须有一条通向源端且不间断的返回路径。

强电场是由微带线和返回平面(或走线)之间的高频数字信号产生的。如果返回路径断开,则电场将依附于最近的金属,这不太可能是想要的返回路径。当未定义返回路径时,电磁场将在整个电介质中“泄漏”并导致共模电流在整个电路板上流动。不受控制的电磁场还会通过耦合到介质层内的导通孔,导致时钟或其他高速信号交叉耦合到同一电介质内的数十条其他电路走线上。由此产生的共模电流往往会耦合到“类似天线的结构”中,例如I/O电缆或屏蔽外壳中的槽/开口,从而导致EMI。

电路板叠层

大多数人都接受过“电路理论”教育,当我们想象返回电流如何流回源端时,曾经学过的理论就变得很重要。但是,我们还需要考虑,信号的能量不仅是电流,还有穿过电介质的电磁波阵面,或者说是“场论”。牢记这两个概念只是在强调设计传输线(与返回路径直接相邻的信号走线)的重要性,而不仅仅是简单的电路走线布线。成功的设计能证实这两种观点。

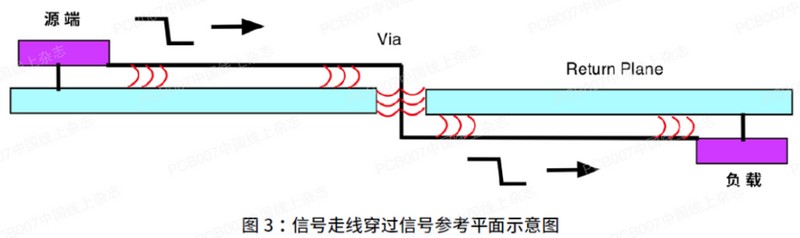

为了满足电路和场论,我们现在了解了电源和电源返回平面相邻以及信号和信号返回平面相邻的重要性。参考单个平面的信号或电源路径始终具有明确的返回至源端的路径。图3所示为电磁场如何保持在电介质内的返回平面两侧。为展示得更加清楚,此处未包含电介质。

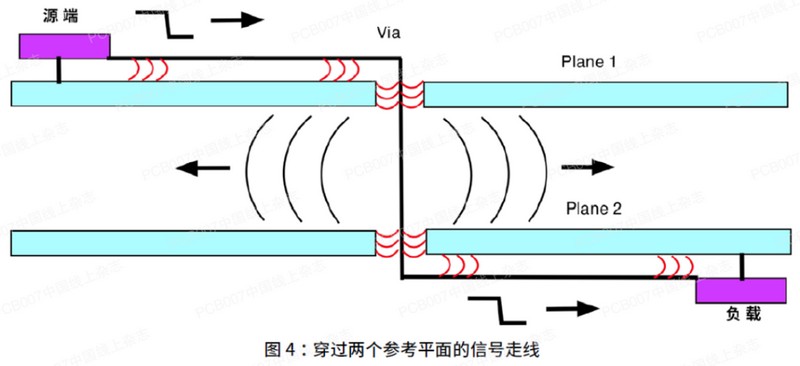

另一方面,如果信号通过两个参考平面(图4),事情就会变得更加棘手。如果两个平面的电位相同(例如,两个平面都是返回平面),则可以在信号导通孔附近添加简单的连接导通孔。这些导通孔会形成一个明确定义的至源端返回路径。

如果参考平面具有相同的电位(例如信号或电源返回路径),则在信号导通孔旁边放置缝合导通孔就足够了。但是,如果平面具有不同的电位(例如电源和返回路径),则必须将缝合电容器安装在非常靠近信号通孔的位置。缺乏定义明确的返回路径将导致图中所示情况,即电磁场在电介质周围泄漏,并耦合到其他信号导通孔或辐射到电路板边缘。

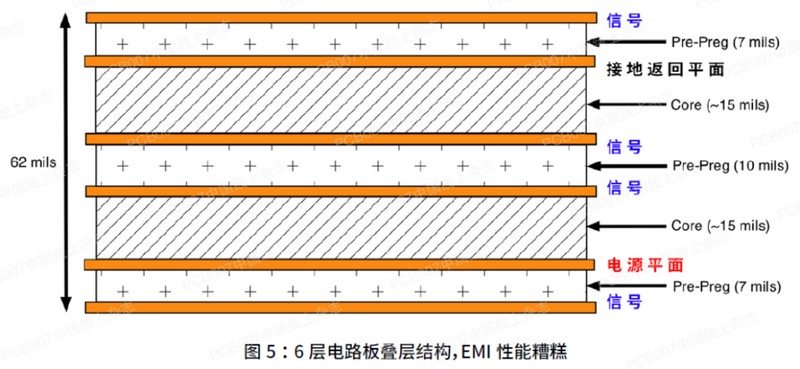

举一个我经常遇到的案例,这是一个糟糕却非常典型的电路板叠层结构(图5)。注意,电源平面和电源返回平面相隔三层。任何PDN瞬变都可能交叉耦合到中间的两个信号层。类似地,很少有信号层具有相邻的返回平面,因此,传播波返回路径将完全跳转到返回至源端路径上位置最近的金属。这种情况会再次在整个电路板上耦合时钟噪声。

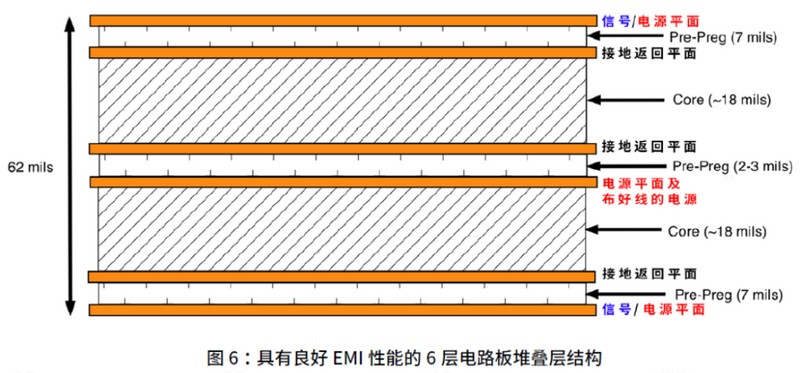

为展示更好的设计,去掉了一个信号层(见图6)。此电路板叠层中,电源平面和电源返回平面是相邻的,每个信号层都有一个相邻的信号(或电源)返回平面。在两个返回平面之间使用多个连接导通孔也是一个好主意,这样能保证返回至源端的路径具有最低阻抗。使用类似设计,EMI性能将得到显著改善。在许多情况下,简单地重新安排叠层结构就可避免辐射干扰。

注意,在顶层和底层之间运行信号时,需要在信号穿透点处的返回平面之间加入“缝合”导通孔,在电源平面和电源返回平面之间加入缝合电容器,从而最大程度地减小返回路径。理想情况下,这些缝合导通孔应位于距每个信号导通孔1~2毫米的范围内。

其他建议

其他设计建议还包括沿电路板的一边放置所有电源和I/O连接器。这样做通常可以减少连接器之间的高频压降,从而最大限度地减少电缆辐射。此外,最好将数字、模拟和RF电路隔离开,因为这样做可以最大限度地减少噪声与敏感电路之间的交叉耦合。当然,高速时钟或类似的高速信号应在尽可能短且直接的路径中运行。这些快速信号不应在电路板较长的边缘运行或通过连接器附近。

Kenneth Wyatt任Wyatt Technical Services LLC公司的首席顾问,并在2016~2018年期间担任《Interference Technology Magazine》的高级技术编辑。他在EMC工程领域工作了30 多年,专门研究产品设计以实现EMC 合规性、EMI故障排除和合规性测试。

由于篇幅有限,本文节选刊登,更多内容请点击这里查看,文章发表于《PCB007中国线上杂志》7月号,更多精彩原创内容,欢迎关注“PCB007中文线上杂志”公众号。