本文的目标是为了阐明可以使用拼接元体来代替传统导通孔技术采用的点到点连接。点到点连接有最好的信号完整性性能(连接中少一个导通孔会使信号失真)。导通孔主要是会引起信号损耗/分散的电容性要素。

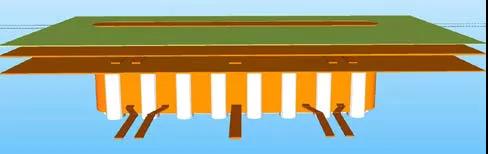

本文将重点介绍开发用于最大程度减少损耗和分散的导通元体。我们将会采用VeCS-2技术(盲孔/混合通孔)结构(图1)。

图1 :多层VeCS-2 技术结构

采用拼接元体孔的优势在于我们可以使用“ 传统”的正交布线方式,这种方式可以高效利用信号层。但是在一些情况下,正交布线或曼哈顿布线法需要使用到较长的走线,所以介电损耗和传导损耗会增加,从而导致整体损耗增加。

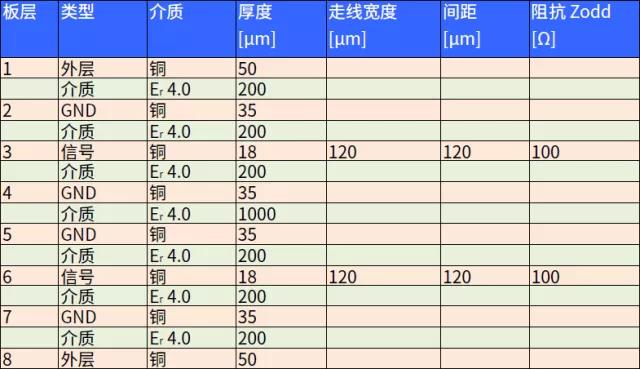

为了模拟拼接元体,我们按照图2所示进行元体设置:一个VeCS-2(盲孔)要素带有8个连接位置——一侧有7个连接点,槽另一侧上有GND基准,为7个连接点提供基准。为了让图示更简洁清晰,我们没有画出所有的基准层。

图2 :拼接元体仿真

5个连接点包括:

1. 一个差分对

2. GND(起到屏蔽作用)

3. 一个单端信号

4. GND(起到屏蔽作用)

5. 一个差分对

GND基准为所有差分对建立了可控阻抗。差分对VeCS 部分的顶部背捞到最短的残余长度。在图3和图4中,我们也展示了二次铣削的特征。二次铣削、顶部与底部的背捞使用的铣刀尺寸都是0.3mm。所有铣削都在同一工艺步骤中进行。

图3 :上板面(S 面)背捞

图4 :捞铣底槽(BR)俯视图

差分对VeCS部分的顶部被回线,以最大程度地分散。

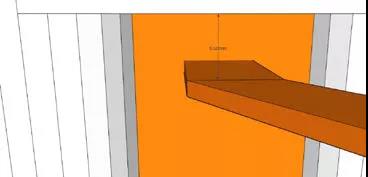

创建的元体为差分对和单端走线建立了埋微带。本实例中的走线宽度是0.12mm;可以调整叠层以达到所要求的差分阻抗。垂直直线的宽度是0.30mm。这样就会形成埋微带结构以及±110欧姆的阻抗(ZOdd)。我们考虑采用介电常数Er为4.0的槽填充材料。

残留长度由槽底的走线与槽底的介质层的厚度及捞底槽后的剩余深度决定(图6)。我们目前设定的最大的残留长度为0.125mm+0.1mm=0.225mm。

图5 :垂直走线和水平走线宽度

图6 :残余长度

在顶部,桩线的最大残余长度为0.125 mm。在此不必包括槽底部的0.1mm。

槽的顶部覆盖电镀铜层(在槽内填充绝缘物质后),如图8所示。

图7 :顶部桩线残余长度

图8 :槽的顶部覆盖电镀铜层

VeCS的元体上背捞后可以选择进行盖帽电镀,图8)。如果进行了盖帽电镀,则会对阻抗产生影响,所以需要将其作为设计参数进行仿真(表1)。

表1 :叠层

可以通过改变电路板中心的介质(厚度1.0 mm)来调整垂直走线的长度,从而确定垂直走线长度对信号性能产生的影响。现在可用作填充物,可以填充于未使用的内层空间从而节省流程。槽使用的填充材料是导通孔填充/填塞油墨。已知频率极限内的性质,可在场解算器模型中用于创建精确的模型。

VeCS缝合要素拼接元体的信号完整性分析

避开连接器或BGA中逃逸是一个复杂因子;也可以创建层间导通体避免同一层上的点到点连接。为了最大程度地降低信号失真/信号反射现象,可用点到点连接方式来支持导通孔与层导通体。在这一部分,我们会分析VeCS-2技术的层间导通体SI性能。

在几乎可以不降低传输线SI性能的基础上可以使用导通体,可以简化很多设计的布线。因此也降低了设计的复杂度(例如层数减少、取消多次压合和消除顺序层压等)。我们使用了“Simbeor THz 2017.01”对SI性能进行分析,在此要特别感谢Yuriy Schlepnev的帮助,他在分析和模拟工具中翻译VeCS设计。

根据机械VeCS-2设计原则创建了以下VeCS要素。每个VeCS中使用一个差分对,其他要素在俯视图中都被遮蔽了(图9)。

图9 :VecS 要素俯视图

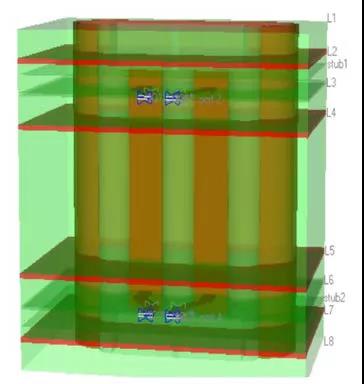

我们创建了一个8层的叠层结构,如图10中的3D图像所示,目标差分阻抗为95欧姆。我们在进行二次铣削去除槽底铜、制造了垂直走线并背捞去除了VeCS走线顶部的桩线。这些操作在一个周期之内就可以全部完成。第3层和第7层是信号层,其他层是基准层。

图10 :8 层叠层结构

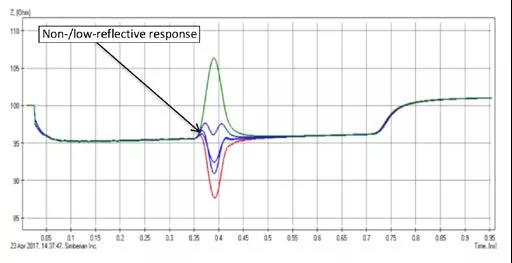

本次分析的第一个目标就是进行时域仿真,并以信号失真程度最低为目标对走线宽度和反焊盘尺寸进行调整。我们先从传统的电容响应开始,按照预期形成一个层层导通体(例如经过导通孔)并朝着平坦线路的方向去调试VeCS要素。如图11所示,对响应做出更多改动之后,从电容元件要素(红线和蓝线)变成了电感要素(绿线)。

图11 :TDR 响应是垂直走线宽度变量的函数

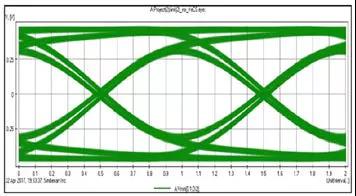

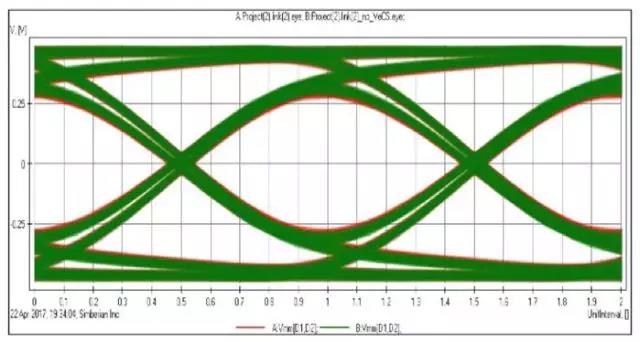

我们使用TD仿真的结果来进行30Gb/s比特流眼图模拟。图12中绿色部分是未调整VeCS要素的参考传输线,图13中红色部分所示是调整VeCS过渡层后的传输线(最佳适配/低反射性TDR)。

图 12 :发射端眼图

图 13 :接收端眼图

在图14中,我们将不带有VeCS(绿色)的传输线眼图叠加在带有VeCS要素(红色)的传输线眼图上。

图14 :发射端眼图与接收端眼图完全重合

使用VeCS后,图像中的眼图更接近;与不使用VeCS的传输线相比,差异非常微小——0.516 V:0.539 V。表2列出了两幅眼图的具体细节。

表2 :仿真性能数据

总结

同时,随着不同项目生产出更多产品,可以确定产品的可靠性并将测量结果与模拟模型匹配。图15是VeCS-2深槽截面示意图,展示出了它的性能。这是HDPUG项目的一部分。

图15 :深VecS-2 槽的截面图

致谢

感谢Simberean公司的Yuriy Shlepnev为本研究仿真工作提供的支持。同时也感谢WUS PCB China的研发团队在VeCS技术方面的杰出研发工作。

编者注:在本篇文章翻译审稿过程中,我们得到了沪士电子技术团队Eddie Mok以及孙丽丽女士的大力协助,还有吴安甫先生的引荐,在此特别感谢!

作者:Joan Tourné,NextGIn Technology 首席执行官

更多内容,可点击在线阅读。